Bộ câu hỏi trắc nghiệm kiến trúc máy tính có đáp án - Phần 5

- 30/08/2021

- 50 Câu hỏi

- 2.5K Lượt xem

Trắc Nghiệm Hay giới thiệu đến các bạn Bộ câu hỏi trắc nghiệm kiến trúc máy tính có đáp án - Phần 5. Tài liệu bao gồm 50 câu hỏi kèm đáp án thuộc danh mục Quản trị hệ thống. Tài liệu này sẽ giúp các bạn ôn tập, củng cố lại kiến thức để chuẩn bị cho các kỳ thi sắp tới. Mời các bạn tham khảo!

Cập nhật ngày

01/09/2021

Thời gian

50 Phút

Tham gia thi

45 Lần thi

Câu 1: Xét sơ đồ phân cấp hệ thống nhớ, phát biểu nào sau đây là sai:

A. Mức thanh ghi là mức trao đổi nhanh nhất

B. Mức thanh ghi là mức trao đổi chậm nhất

C. Mức cache được chia thành hai mức

D. Mức cache là mức gần thanh ghi nhất

Câu 2: Xét sơ đồ phân cấp hệ thống nhớ, phát biểu nào sau đây là đúng:

A. Từ bộ nhớ cache đến bộ nhớ ngoài, tốc độ nhanh dần

B. Từ thanh ghi đến bộ xử lý, tốc độ tăng dần

C. Từ bộ nhớ ngoài đến thanh ghi, dung lượng giảm dần

D. Từ bộ nhớ trong đến bộ nhớ cache, tần suất truy nhập giảm dần

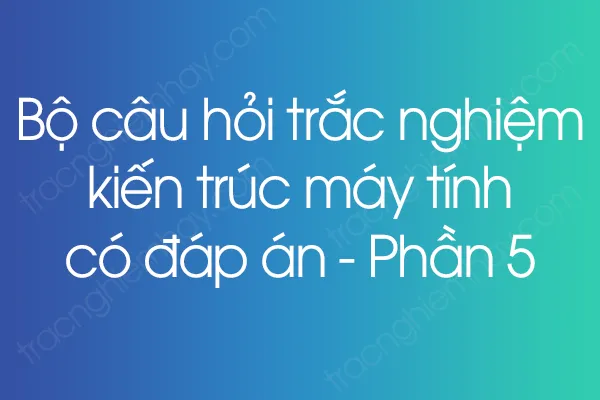

Câu 3: Cho chip nhớ như hình vẽ, đây là ký hiệu của:

A. SRAM 4K x 8 bit

B. DRAM 4 K x 8 bit

C. SRAM 2K x 8 bit

D. DRAM 2 K x 8 bit

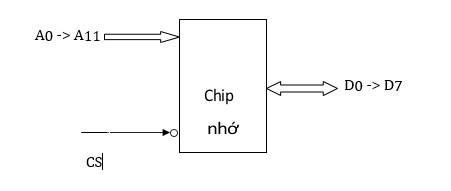

Câu 4: Cho chip nhớ như hình vẽ, đây là ký hiệu của:

A. SRAM 8K x 16 bit

B. DRAM 8K x 16 bit

C. SRAM 64M x 16 bit

D. DRAM 64M x 16 bit

Câu 5: Đối với bộ nhớ chính (BNC) máy tính, phát biểu nào sau đây là sai:

A. Chứa các chương trình và dữ liệu dưới dạng thư viện

B. Về nguyên tắc, người lập trình có thể can thiệp vào toàn bộ BNC

C. Việc quản lý logic BNC tuỳ thuộc vào từng hệ điều hành

D. Được đánh địa chỉ trực tiếp bởi bộ xử lý

Câu 6: Đối với bộ nhớ chính (BNC) máy tính, phát biểu nào sau đây là đúng:

A. Việc đánh địa chỉ cho BNC tuỳ thuộc vào từng hệ điều hành

B. BNC do bộ xử lý đánh địa chỉ trực tiếp

C. Có những loại máy tính không có BNC

D. Các ngăn nhớ không tổ chức theo byte

Câu 7: Đối với bộ nhớ cache, phát biểu nào sau đây là đúng:

A. Cache có thể được đặt trên cùng chip với CPU

B. Bộ nhớ chính có tốc độ nhanh hơn cache

C. Bộ nhớ cache được đặt giữa bộ nhớ chính và bộ nhớ ngoài

D. Cache không được đặt trên cùng chip với CPU

Câu 8: Đối với bộ nhớ cache, phát biểu nào sau đây là đúng:

A. Bộ nhớ ngoài nhận cả khối dữ liệu từ cache

B. Truyền dữ liệu giữa CPU và cache theo đơn vị khối nhớ

C. Truyền dữ liệu giữa CPU và cache theo đơn vị từ nhớ

D. Khi cần, CPU nhận dữ liệu trực tiếp từ bộ nhớ chính

Câu 9: Khi CPU truy nhập cache, có hai khả năng sau:

A. Trượt cache, trúng cache

B. Sai cache, đúng cache

C. Trên cache, dưới cache

D. Trong cache, ngoài cache

Câu 10: Cache hoạt động nhờ vào nguyên lý:

A. Nguyên lý hoạt động của máy tính

B. Nguyên lý điều khiển ghi dữ liệu

C. Nguyên lý điều khiển đọc dữ liệu

D. Nguyên lý định vị tham số bộ nhớ

Câu 11: Trong sự trao đổi giữa cache và bộ nhớ chính, phát biểu nào sau đây là sai:

A. Bộ nhớ chính chia thành các block nhớ

B. Cache chia thành các line nhớ

C. Bộ nhớ chính chia thành các line nhớ

D. Kích thước line bằng kích thước block

Câu 12: Xét bộ nhớ cache, mỗi line được gắn thêm Tag là để:

A. Xác định block nào của bộ nhớ chính đang ở trong line

B. Xác định cache có dung lượng bao nhiêu

C. Xác định line có dung lượng bao nhiêu

D. Xác định cache có bao nhiêu line

Câu 13: Xét bộ nhớ cache, có các kỹ thuật ánh xạ địa chỉ sau đây:

A. Trực tiếp, liên kết hoàn toàn, liên kết tập hợp

B. Liên kết hoàn toàn, liên kết phụ thuộc, gián tiếp

C. Liên kết tập hợp, liên kết phần tử, gián tiếp

D. Trực tiếp, liên kết phần tử, liên kết gián đoạn

Câu 14: Trong kỹ thuật ánh xạ liên kết hoàn toàn, các trường địa chỉ là:

A. Tag + Word + Line

B. Tag + Word

C. Tag + Line + Word

D. Tag + Line

Câu 15: Trong kỹ thuật ánh xạ trực tiếp, các trường địa chỉ là:

A. Tag + Word + Line

B. Tag + Word

C. Tag + Line + Word

D. Tag + Line

Câu 16: Trong kỹ thuật ánh xạ liên kết tập hợp, các trường địa chỉ là:

A. Tag + Word + Set

B. Tag + Word

C. Tag + Set + Word

D. Tag + Set

Câu 17: Cho máy tính có dung lượng bộ nhớ chính: 128MB, cache: 64KB, line: 8 byte, độ dài ngăn nhớ: 1 byte. Trong trường hợp kỹ thuật ánh xạ trực tiếp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

A. 12 + 10 + 5

B. 13 + 10 + 4

C. 14 + 11 + 2

D. 14 + 10 + 3

Câu 18: Cho máy tính có dung lượng bộ nhớ chính: 256MB, cache: 128KB, line: 16 byte, độ dài ngăn nhớ: 2 byte. Trong trường hợp kỹ thuật ánh xạ trực tiếp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

A. 11 + 13 + 3

B. 11 + 14 + 2

C. 12 + 13 + 4

D. 12 + 12 + 3

Câu 19: Cho máy tính có dung lượng bộ nhớ chính: 512MB, cache: 128KB, line: 64 byte, độ dài ngăn nhớ: 4 byte. Trong trường hợp kỹ thuật ánh xạ trực tiếp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

A. 11 + 11 + 5

B. 12 + 11 + 4

C. 12 + 12 + 3

D. 11 + 12 + 4

Câu 22: Cho máy tính có dung lượng bộ nhớ chính: 128MB, cache: 64KB, line: 16 byte, độ dài ngăn nhớ: 1 byte, set: 4 line. Trong trường hợp kỹ thuật ánh xạ liên kết tập hợp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

A. 13 + 10 + 4

B. 13 + 9 + 5

C. 14 + 9 + 4

D. 14 + 10 + 4

Câu 23: Cho máy tính có dung lượng bộ nhớ chính: 512MB, cache: 128KB, line: 32 byte, độ dài ngăn nhớ: 2 byte, set: 4 line. Trong trường hợp kỹ thuật ánh xạ liên kết tập hợp, dạng địa chỉ do bộ xử lý phát ra để truy nhập cache là:

A. 12 + 12 + 4

B. 13 + 11 + 4

C. 14 + 10 + 4

D. 13 + 9 + 6

Câu 25: Xét kỹ thuật ánh xạ trực tiếp khi truy nhập cache, thứ tự tìm block trong cache được thực hiện dựa theo các trường trong địa chỉ do CPU phát ra như sau:

A. Line -> Tag -> Word

B. Line -> Word -> Tag

C. Tag -> Line -> Word

D. Tag -> Word -> Line

Câu 26: Đối với bộ nhớ cache, xét kỹ thuật ánh xạ liên kết tập hợp, thứ tự tìm block trong cache được thực hiện dựa theo các giá trị trong địa chỉ do CPU phát ra như sau:

A. Word -> Set -> Tag

B. Set -> Word -> Tag

C. Set -> Tag -> Word

D. Word -> Tag -> Set

Câu 27: Xét các thuật toán thay thế dữ liệu trong cache, phát biểu nào sau đây là đúng:

A. Không có thuật toán

B. Ánh xạ trực tiếp không có thuật toán thay thế

C. Hai ánh xạ liên kết (hoàn toàn và tập hợp) có 4 thuật toán

D. Cả b và c đều đúng

Câu 28: Đối với bộ nhớ cache, các thuật toán thay thế dữ liệu là:

A. Ngẫu nhiên, FIFO, LRU, LFU

B. Ngẫu nhiên, LIFO, LRU, LFU

C. Ngẫu nhiên, FIFO, LFU, LTU

D. Ngẫu nhiên, LIFO, LTU, LVU

Câu 29: Đối với các phương pháp ghi dữ liệu vào cache, phát biểu nào sau đây là sai: ![]()

A. Write through: ghi đồng thời vào cả cache và bộ nhớ chính

B. Write back: chỉ ghi vào cache, khi block tương ứng bị thay thế thì mới ghi vào bộ nhớ chính

C. Cả a và b đều đúng

D. Cả a và b đều sai

Câu 30: Đối với các phương pháp ghi dữ liệu vào cache, phát biểu nào sau đây là đúng:

A. Write back: ghi đồng thời vào cả cache và bộ nhớ chính

B. Write through: chỉ ghi vào cache, khi block tương ứng bị thay thế thì mới ghi vào bộ nhớ chính

C. Cả a và b đều không đúng

D. Cả a và b đều đúng

Câu 31: Đối với các thuật toán (TT) thay thế dữ liệu trong cache, phát biểu nào sau đây là đúng:

A. FIFO là TT thay đi block mới nhất trong các block hiện nay

B. LRU là TT thay đi block có tần suất truy nhập ít nhất

C. LFU là TT thay đi block truy nhập gần đây ít nhất

D. Tất cả đều sai

Câu 32: Đối với các thuật toán (TT) thay thế dữ liệu trong cache, phát biểu nào sau đây là sai:

A. FIFO là TT thay đi block cũ nhất trong các block hiện nay

B. FIFO là TT thay đi block có tần suất truy nhập ít nhất

C. LRU là TT thay đi block truy nhập gần đây ít nhất

D. Random là TT thay đi block ngẫu nhiên

Câu 33: Đối với các thuật toán (TT) thay thế dữ liệu trong cache, phát biểu nào sau đây là đúng: ![]()

A. LIFO là TT thay đi block cũ nhất trong các block hiện nay

B. LTU là TT thay đi block có tần suất truy nhập ít nhất

C. LVU là TT thay đi block truy nhập gần đây ít nhất

D. Tất cả đều sai

Câu 34: Đối với các thuật toán (TT) thay thế dữ liệu trong cache, phát biểu nào sau đây là sai:

A. TT Random cho tỉ lệ cache hit thấp nhất

B. TT LRU cho tỉ lệ cache hit cao nhất

C. TT FIFO cho tỉ lệ cache hit cao nhất

D. TT LFU cho tỉ lệ cache hit tương đối cao

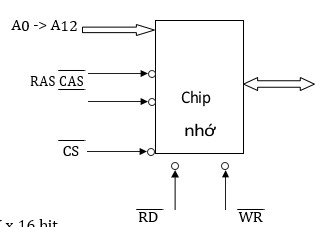

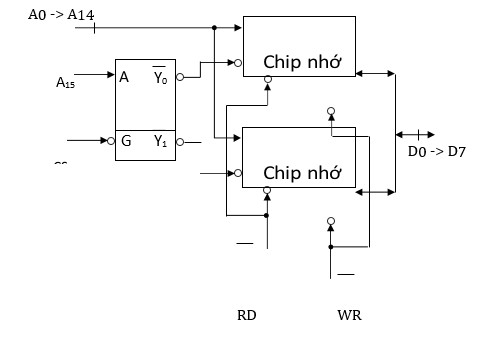

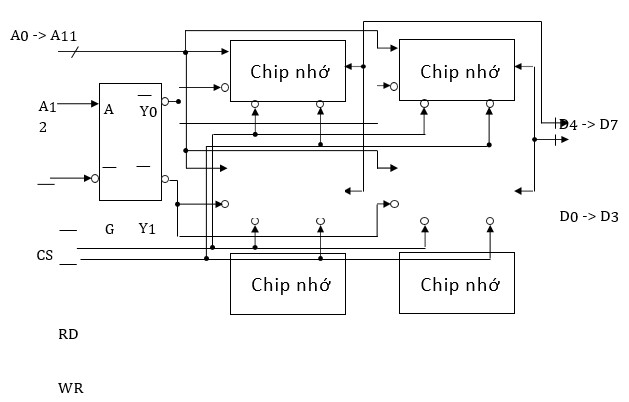

Câu 35: Hình vẽ dưới đây là sơ đồ kết nối của 2 IC SRAM:

A. 4K x 4 bit để có modul nhớ 8K x 4 bit

B. 8K x 4 bit để có modul nhớ 16K x 4 bit

C. 8K x 4 bit để có modul nhớ 8K x 8 bit

D. 4K x 4 bit để có modul nhớ 4K x 8 bit

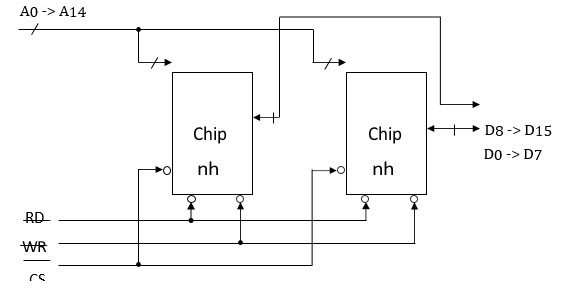

Câu 36: Hình vẽ dưới đây là sơ đồ kết nối của 2 IC SRAM:

A. 32K x 8 bit để có modul nhớ 32K x 16 bit

B. 16K x 8 bit để có modul nhớ 32K x 8 bit

C. 32K x 4 bit để có modul nhớ 32K x 8 bit

D. 16K x 16 bit để có modul nhớ 32K x 16 bit

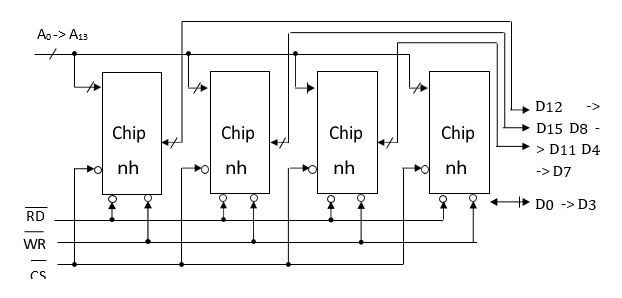

Câu 37: Hình vẽ dưới đây là sơ đồ kết nối của 4 IC SRAM:

A. 32K x 8 bit để có modul nhớ 32K x 16 bit

B. 16K x 4 bit để có modul nhớ 32K x 8 bit

C. 16K x 4 bit để có modul nhớ 16K x 16 bit

D. 32K x 4 bit để có modul nhớ 32K x 16 bit

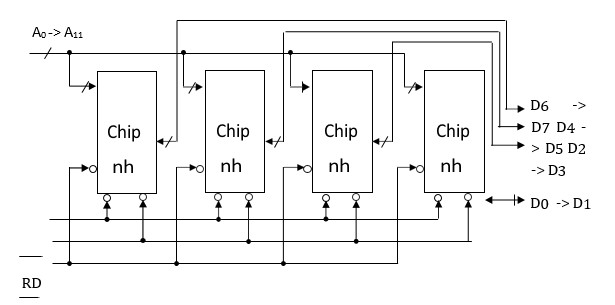

Câu 38: Hình vẽ dưới đây là sơ đồ kết nối của 4 IC SRAM:

A. 4K x 4 bit để có modul nhớ 4K x 8 bit

B. 4K x 2 bit để có modul nhớ 4K x 8 bit

C. 8K x 4 bit để có modul nhớ 8K x 8 bit

D. 8K x 2 bit để có modul nhớ 16K x 2 bit

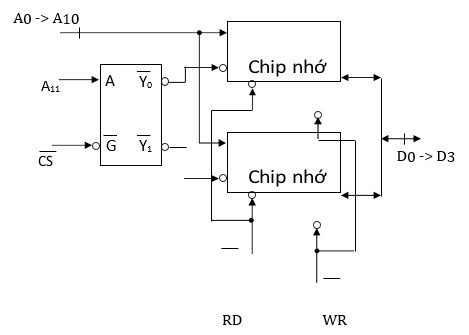

Câu 39: Hình vẽ dưới là sơ đồ kết nối của 2 IC SRAM:

A. 2K x 4 bit để có modul nhớ 4K x 4 bit

B. 2K x 4 bit để có modul nhớ 4K x 8 bit

C. 2K x 4 bit để có modul nhớ 2K x 8 bit

D. 4K x 4 bit để có modul nhớ 8K x 4 bit

Câu 40: Hình vẽ dưới là sơ đồ kết nối của 2 IC SRAM:

A. 32K x 8 bit để có modul nhớ 32K x 16 bit

B. 16K x 8 bit để có modul nhớ 32K x 8 bit

C. 32K x 8 bit để có modul nhớ 64K x 16 bit

D. 32K x 8 bit để có modul nhớ 64K x 8 bit

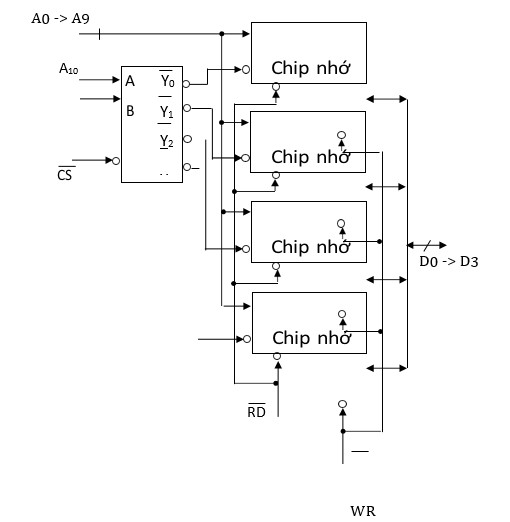

Câu 41: Hình vẽ dưới là sơ đồ kết nối của 4 IC SRAM:

A. 2K x 8 bit để có modul nhớ 8K x 8 bit

B. 2K x 4 bit để có modul nhớ 8K x 8 bit

C. 1K x 4 bit để có modul nhớ 4K x 4 bit

D. 1K x 4 bit để có modul nhớ 4K x 8 bit

Câu 42: Hình vẽ dưới là sơ đồ kết nối của 4 IC SRAM:

A. 4K x 8 bit để có modul nhớ 16K x 8 bit

B. 8K x 8 bit để có modul nhớ 32K x 8 bit

C. 8K x 8 bit để có modul nhớ 16K x 8 bit

D. 8K x 16 bit để có modul nhớ 16K x 16 bit

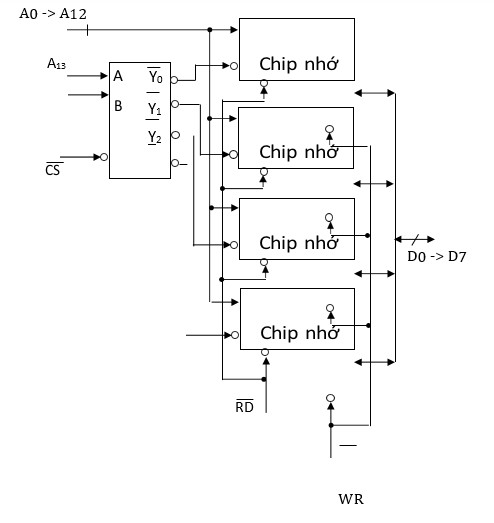

Câu 43: Hình vẽ dưới đây là sơ đồ kết nối 4 IC SRAM:

A. 8K x 4 bit để có modul nhớ 16K x 8 bit

B. 8K x 4 bit để có modul nhớ 16K x 4 bit

C. 8K x 8 bit để có modul nhớ 16K x 8 bit

D. 8K x 8 bit để có modul nhớ 16K x 16 bit

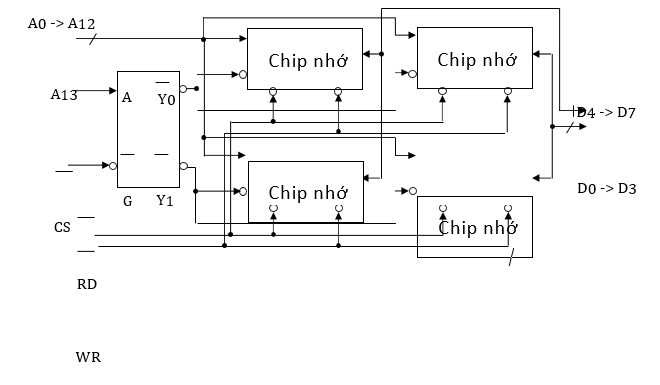

Câu 44: Hình vẽ dưới đây là sơ đồ kết nối 4 IC SRAM:

A. 4K x 4 bit để có modul nhớ 16K x 8 bit

B. 8K x 8 bit để có modul nhớ 8K x 16 bit

C. 8K x 8 bit để có modul nhớ 16K x 8 bit

D. 4K x 4 bit để có modul nhớ 8K x 8 bit

Câu 45: Với chip nhớ SRAM có n đường địa chỉ, m đường dữ liệu thì dung lượng của chip là:

A. 2m x n bit

B. 2n x m bit

C. 2m x n byte

D. 2n x m byte

Câu 46: Với chip nhớ SRAM có n đường địa chỉ, m đường dữ liệu thì dung lượng của chip là:

A. 2m x n bit

B. 22n x m bit

C. 22m x n bit

D. 2n x m bit

Câu 47: Với chip nhớ DRAM có n đường địa chỉ, m đường dữ liệu thì dung lượng của chip là:

A. 22m x n bit

B. 22n x m bit

C. 22m x n byte

D. 22n x m byte

Câu 48: Với chip nhớ DRAM có n đường địa chỉ, m đường dữ liệu thì dung lượng của chip là:

A. 2m x n bit

B. 22n x m bit

C. 22m x n bit

D. 2n x m bit

Câu 49: Đối với bộ nhớ cache, xét nguyên lý định vị về thời gian, phát biểu nào sau đây là đúng:

A. Thông tin vừa truy nhập thì xác suất bé là sau đó nó sẽ được truy nhập lại

B. Thông tin vừa truy nhập thì xác suất lớn là sau đó nó sẽ được truy nhập lại

C. Thông tin vừa truy nhập thì sau đó chắc chắn nó sẽ không được truy nhập lại

D. Thông tin vừa truy nhập thì chắc chắn là sau đó nó được truy nhập lại

Câu 50: Đối với bộ nhớ cache, xét nguyên lý định vị về không gian, phát biểu nào sau đây là đúng:

A. Mục thông tin vừa truy nhập thì xác suất lớn là sau đó các mục lân cận được truy nhập

B. Mục thông tin vừa truy nhập thì xác suất bé là sau đó các mục lân cận được truy nhập

C. Mục thông tin vừa truy nhập thì chắc chắn là sau đó các mục lân cận được truy nhập

D. Thông tin vừa truy nhập thì chắc chắn là sau đó các mục lân cận không được truy nhập

Chủ đề: Bộ câu hỏi trắc nghiệm kiến trúc máy tính có đáp án Xem thêm...

- 45 Lượt thi

- 50 Phút

- 50 Câu hỏi

- Người đi làm

Cùng chủ đề Bộ câu hỏi trắc nghiệm kiến trúc máy tính có đáp án

- 1.6K

- 55

- 50

-

94 người đang thi

- 1.2K

- 9

- 50

-

98 người đang thi

- 1.2K

- 6

- 50

-

41 người đang thi

- 1.7K

- 6

- 50

-

25 người đang thi

Chia sẻ:

Đăng Nhập để viết bình luận